Nudestix. Effortless beauty.

What we did : Custom Shopify 2.0 theme with complex integrations and customer focused features.

Impact : The digital transformation yielded remarkable results. Nudestix experienced a substantial upswing in customer engagement, e-commerce conversions, and revenue. This surge in business performance has catapulted Nudestix to the forefront, marking it as one of the world’s fastest-growing makeup startups.

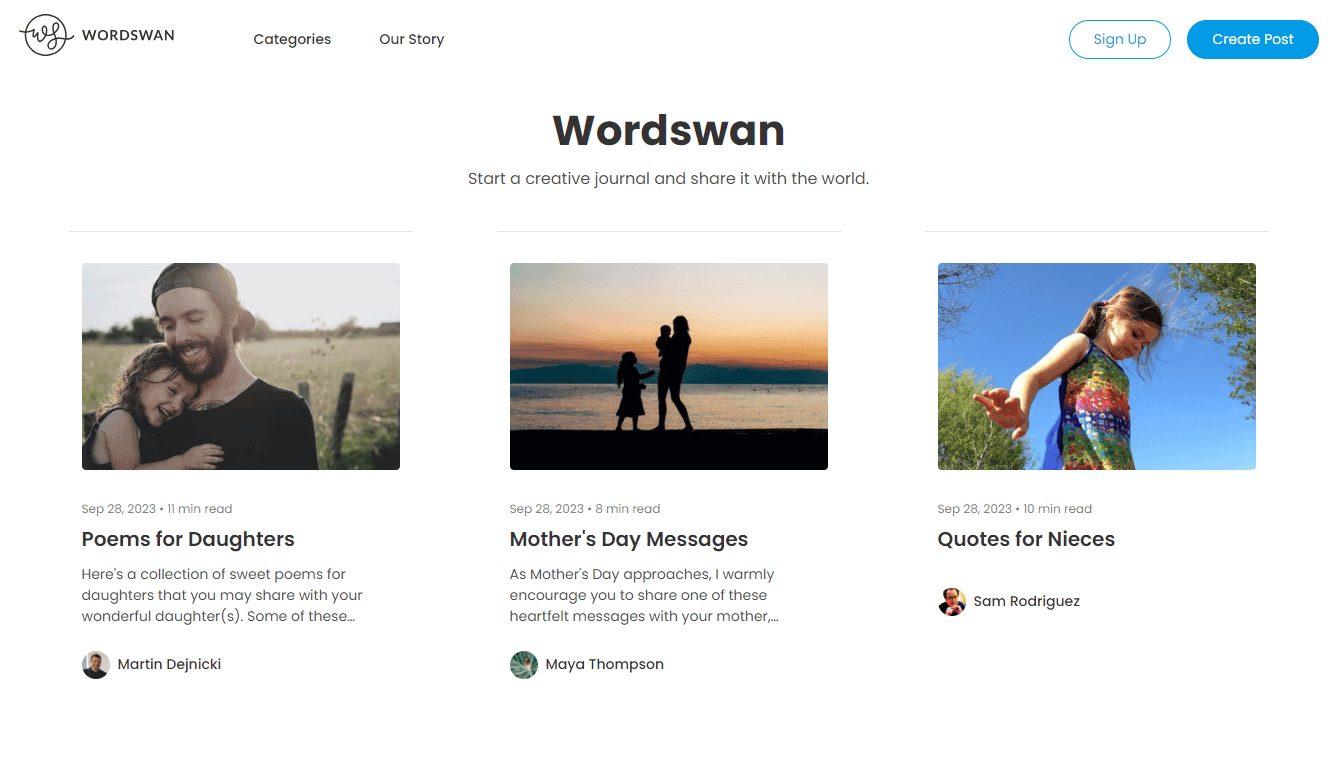

Wordswan. Ignite emotions.

What we did : A bespoke publishing platform that empowers users to curate personal journals, or share their writings with the world.

Impact : Wordswan isn’t just another digital product; it’s an internal passion project. It showcases our capability to develop user-centric content management systems and visually captivating progressive web apps. As a PWA, Wordswan promises and delivers an optimal user interaction experience, characterized by intuitive navigation, swift responses, and elegant design. Every feature is fine-tuned to ensure that creativity meets visibility, and expressions find their deserving audience, seamlessly.

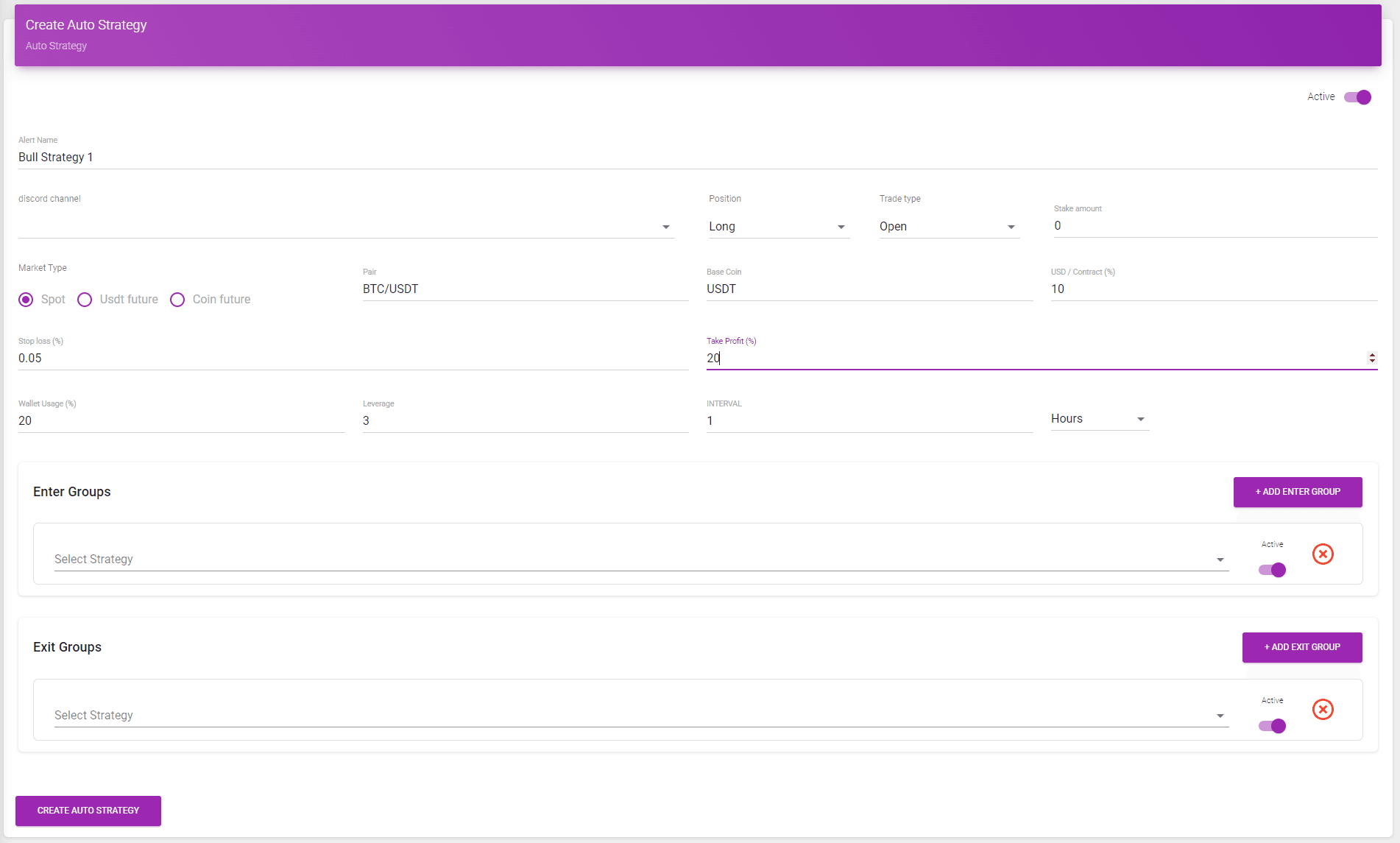

Edgecharts. Quant trading edge.

What we did : A cutting-edge quantitative trading platform that empowers users to construct and execute automated trading strategies effortlessly and gain market insights without writing a single line of code.

Impact : With Edgecharts, we efficiently assessed over 300 intricate trading strategies in just a few months. The most effective ones ascended to production and are currently yielding profitable results. Our relentless innovation in the algorithmic trading space drives us as we are looking to evolve Edgecharts into the most powerful quantitative trading platform in the world.

Power BI. Power BI for Munich RE

What we did : We delivered comprehensive analytics implementation guidelines and strategized to optimize the tracking of marketing, sales, and product attribution strategies. Our expertise extended to the creation of advanced visualizations using PowerBI, facilitated by API integrations with various CRMs and Google Analytics. The synergy of advanced SQL queries and scripts were instrumental in refining data sets, ensuring that in-house visualization tools are fed with accurate and insightful data.

Impact : Our tailored analytics and visualization solutions empowered sales, product, and marketing teams with real-time, actionable insights, enhancing decision-making efficiency and strategic agility. The implementation of our guidelines led to improved data accuracy, in-depth insights, and enriched team collaborations. The initiative underscored our capability to transform raw data into strategic assets, elevating organizational performance and insight-driven decision-making processes.

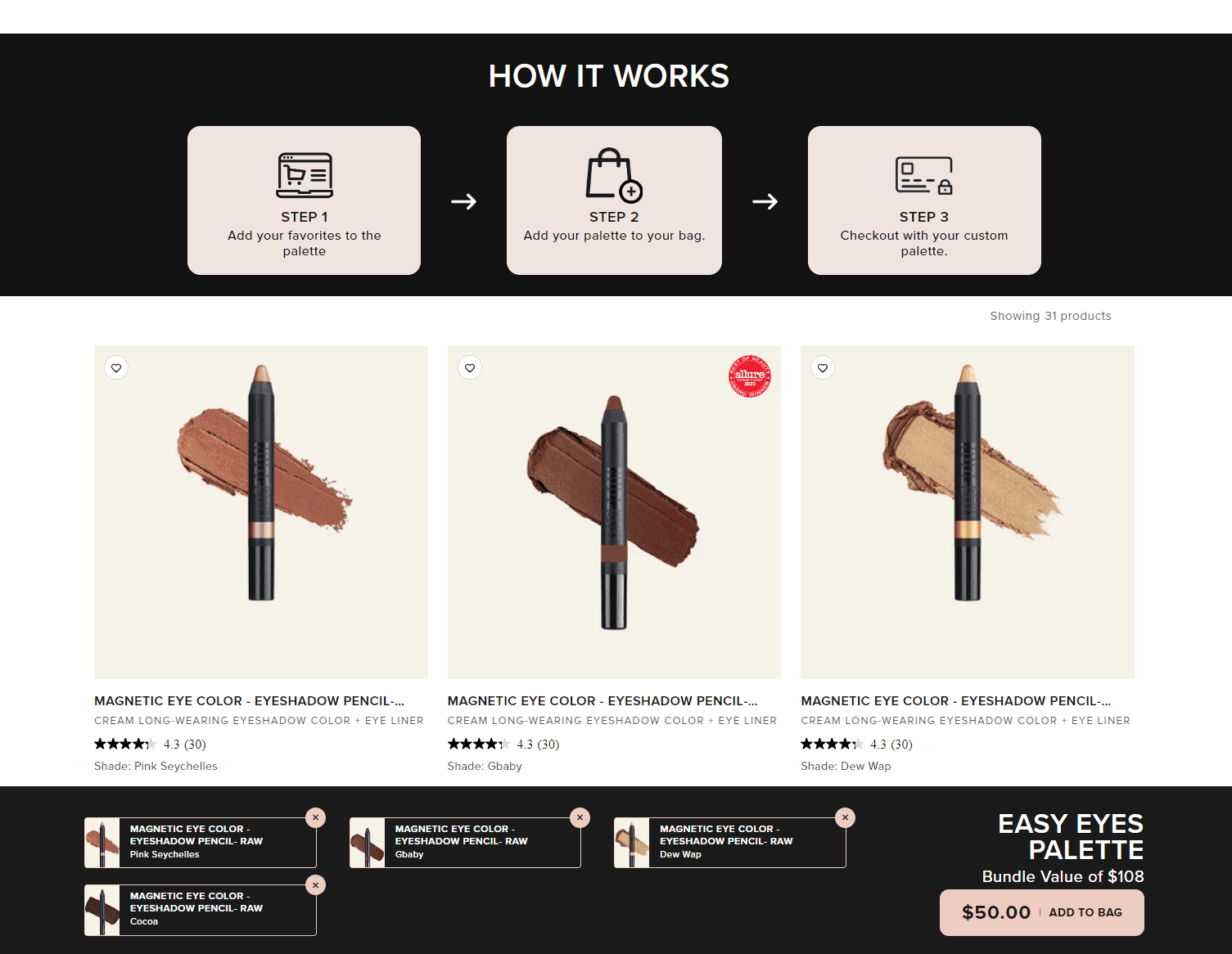

Bundle Builder. Pick-a-Palette. Custom Shopify Experience.

What we did : We created a custom Shopify experience for Nudestix, enabling customers to effortlessly build customized product bundles. Users can add, edit, or remove items in real-time without page refreshes for a seamless experience. Admins enjoy flexibility with customizable and replicable bundle options, and a specialized checkout application transforms bundle orders into clear line items for efficient warehouse processing.

Impact : Customers relish an intuitive, uninterrupted bundle customization journey, boosting engagement and satisfaction. For Nudestix, the feature offers adaptability for varied offerings and promotions, streamlining operations. This innovation highlights our knack for melding user-centric design with operational efficiency, crafting tailored solutions that elevate brand engagement and inventory management.

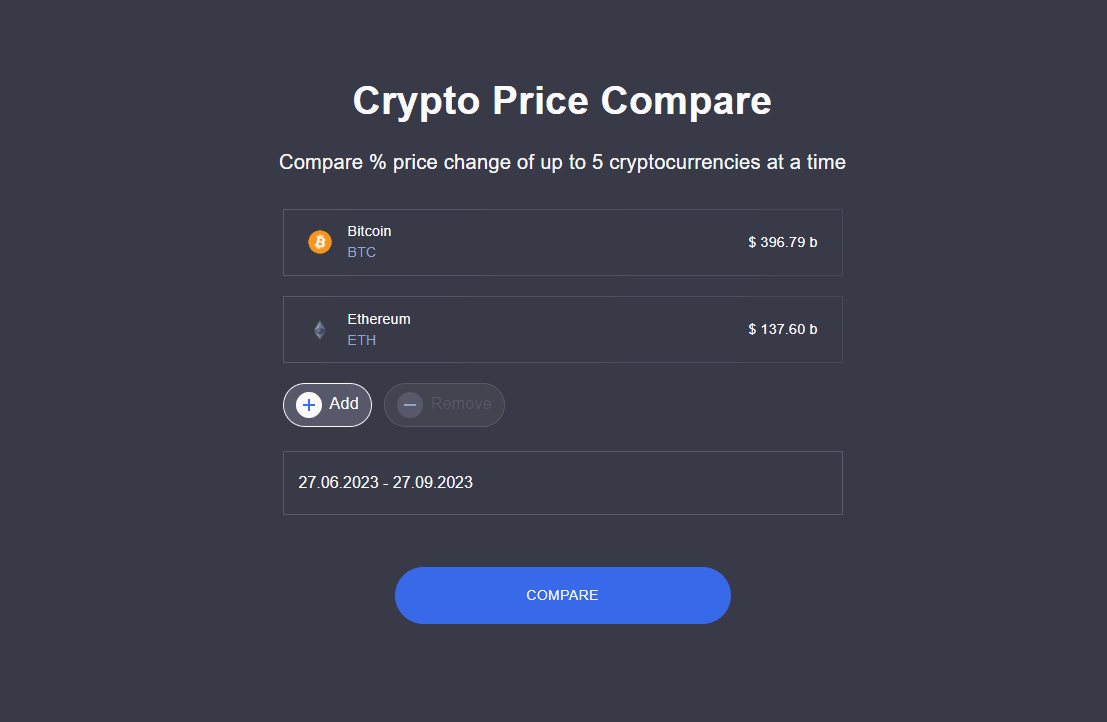

Exwhere. Navigate Cryptos.

What we did : We designed and developed Exwhere, an API-driven web application tailored for effortless cryptocurrency discovery and analysis. It equips users with intuitive tools to pinpoint where to acquire desired cryptocurrencies, utilizing an algorithm centered on trust and liquidity. The built-in comparison tool further enhances user experience by enabling a meticulous analysis of price fluctuations across multiple cryptocurrencies.

Impact : Exwhere has emerged as a pivotal resource for cryptocurrency enthusiasts and investors, offering streamlined access and insights into the dynamic world of digital currencies. The trust and liquidity-focused algorithm ensures users are directed to reliable and liquid platforms, instilling confidence in their purchasing decisions. The comparison tool enriches the decision-making process by providing real-time data on price variations, fostering informed and strategic investments.

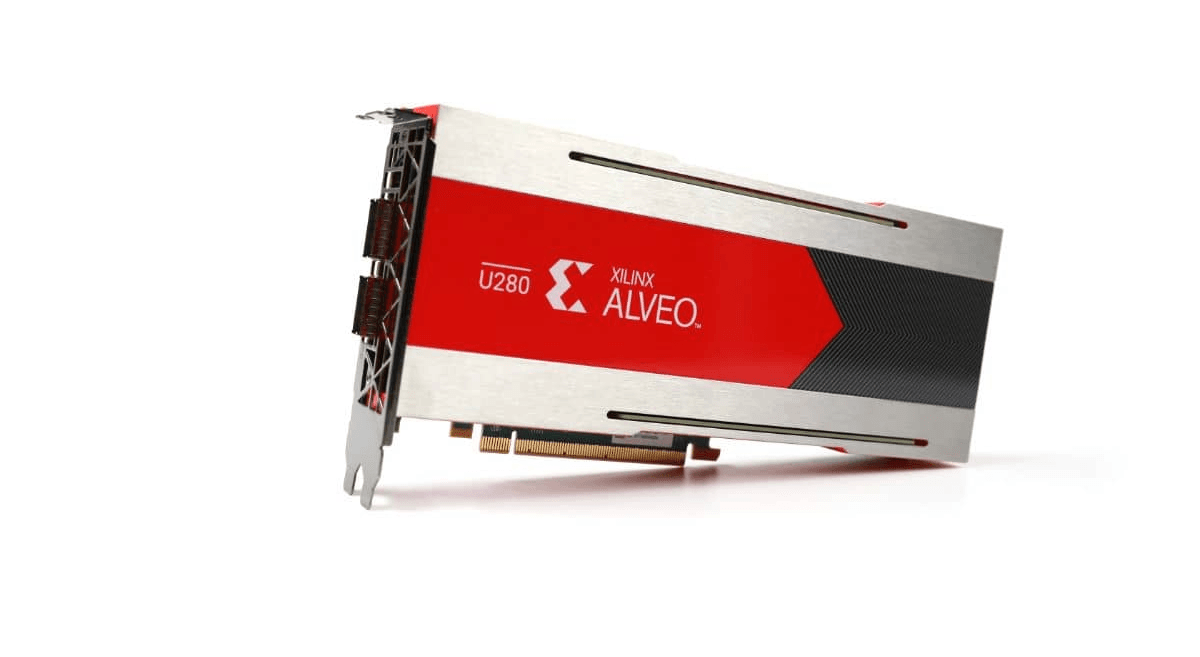

FPGA Development. Project Titan: Revolutionizing Cryptocurrency Mining

What we did : Worked closely with a client on Project Titan, an advanced FPGA configuration crafted for optimal cryptocurrency mining. Developed on the Xilinx Virtex UltraScale+ FPGA BCU1525 Kit, Titan integrates RTL designs like SHA-256 and Keccak, achieving clock speeds of 550MHz and optimal throughput.

Impact : Titan has accelerated cryptocurrency mining efficiency and output, positioning the proprietary technology as a benchmark in the blockchain ecosystem. The project highlights our capability to innovate and underscores the role of optimized FPGA in enhancing blockchain scalability and energy efficiency globally.